AT&S Technologieforum zeigt Lösungen für die Herausforderungen von morgen auf

- Leiterplatten-Spezialist präsentiert innovative Technologien und Trends vor etwa 150 Teilnehmern

- Miniaturisierung und Modularisierung prägen die Zukunft der Verbindungstechnik

Zeltweg, Leoben – Auf dem Red Bull-Ring in Zeltweg, wo sich sonst Formel 1-Wagen spannende Rennen liefern, präsentierte AT&S im Rahmen des 13. AT&S Technologieforums Spitzen-Technologie und spannende Trends rund um Verbindungslösungen. Eine Rekordbeteiligung von etwa 150 Kunden informierte sich über die neuesten Entwicklungen in der Elektronik- und Leiterplattenindustrie für die Bereiche Automotive-, Industrie- und Medizintechnik. Im Fokus der breit gefächerten Vorträge standen globale Megatrends und ihre Auswirkungen auf die Elektronikindustrie.

Miniaturisierung und Modularisierung sind die Schlüsselbegriffe in der Verbindungstechnik, das wurde auch in der Keynote von Heinz Moitzi, COO AT&S deutlich. Was Aristoteles mit „Das Ganze ist mehr als die Summe der einzelnen Teile“ umschrieb, fasste Moitzi in der Formel 1+1 = 3 zusammen. Miniaturisierung kann nur durch immer höhere Packungsdichten der elektronischen Module erreicht werden, wobei Leiterplatten- und Halbleiter-Technologien verschmelzen. Dafür bietet AT&S eine Kombination von bestehenden mit neuen Technologien, die ideal aufeinander abgestimmt sind. So werden„Advanced Packaging“-Lösungen ermöglicht, die extrem kompakt und energieeffizient sind. Am Ende dieser Entwicklung steht dann das All-in-one-Package.

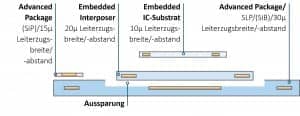

Die fortschreitende Miniaturisierung führte Hannes Vorarberger, Group Manager R&D, weiter aus, gemäß der Frage „Was kommt nach dem Gesetz von Moore?“. Während man mit Anylayer-Leiterplatten und Substraten derzeit Leiterbahnbreiten von ca. 40 µm erreicht, geht der Trend in Richtung 10 µm und darunter. Dafür werden neben subtraktiven auch additive Technologien wie MSAP (Modified Semi-Additive Process) genutzt. Bei AT&S wird intensiv an bisher limitierenden Faktoren wie dem gezielten Ätzen oder der Rauheit der Kupferfolien geforscht, um die weitere Miniaturisierung voranzutreiben.

Die Leiterplatten-Technologie ist auch durch die steigenden Anforderungen an die Basismateralien gekennzeichnet. Walter Pessl, Quality Supplier Engineering bei AT&S, betonte hier u.a. die steigenden thermischen Anforderungen, komplexeren Aufbauten, das Handling von verschiedenen Spannungen und Abständen sowie die Signalintegrität. Gerade High-Speed- und HF-Applikationen haben hier hohe Ansprüche. Bei AT&S wird hier intensiv daran gearbeitet, die maximalen Betriebstemperaturen (MOT) zu erhöhen (z.B. mit FR15 auf 150°C), die Löt-Zuverlässigkeit zu verbessern sowie die CAF (Conductive Anodic Filament)-Festigkeit zu erhöhen. Dafür wurden und werden umfangreiche Untersuchungen mit verschiedenen Materalien durchgeführt.

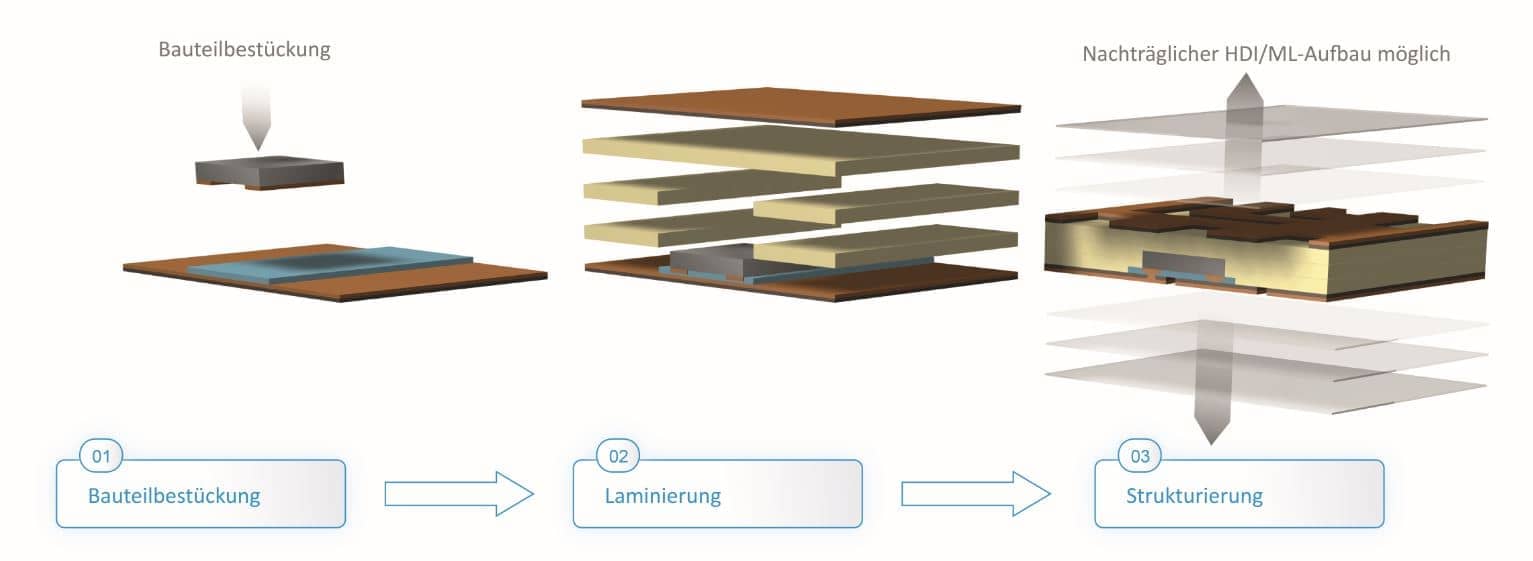

Ein Schwerpunktthema am Technologieforum bildete das „Advanced Packaging“ – innovative, verfahrenstechnische Lösungen für Komponenten- und Halbleiter-Packaginglösungen – von derzeit 2D-Packages zu 3D-Packages, bei der die Komponenten in mehreren Schichten horizontal und vertikal zu einem einzigen Schaltkreis verbunden sind. Johannes Stahr, Group Manager Technology, zeigte dabei die Entwicklung der Embedded-Technologie bei AT&S auf, beginnend mit der Einbettung von passiven Komponenten bis hin zu ECP® (Embedded Component Packaging) für System-in-Boards (SiB) und System-in-Packages (SiP). Mittlerweile liefert AT&S ECP-Produkte bereits in Serienfertigung, mit zahlreichen bereits realisierten Produkten, von Computer-Boards über medizinische Sensor-Produkte bis hin zu MEMS-Mikrophonen. Außerdem arbeitet AT&S mit Partnern intensiv an Embedded-Power-Produkten. So konnte u.a. ein 500-W-Pedelec-Demonstrator unter Einbettung von MOSFETs, passiven Komponenten und Logikschaltungen realisiert werden werden. Umfangreiche Tests belegen die hohe thermische und Schock-Performance sowie das ausgezeichnete Schaltverhalten des Designs. Im nächsten Schritt sind noch leistungsfähigere Module im High-Power-Bereich geplant.

AT&S Embedded Component Packaging Technology (ECP)

Flexibilität, Miniaturisierung, Module und Packages, hohe Datenraten und hohe Frequenzen, Leistungselektronik mit hohen Strömen und steigende thermische Anforderungen sowie optimierte Fertigungsprozesse stellen nach Hannes Vorarberger die Herausforderungen, aber auch Chancen der Elektronik-Industrie in den kommenden Jahren dar. AT&S ist bestens aufgestellt, um diesen Herausforderungen zu begegnen. Als Beispiele nannte Vorarberger die flexible Integration von mehr Funktionalität, wie mit der Einbettung von Cavities in MEMS-Applikationen, die Kombination von starren mit flexiblen Leiterplatten oder das X-in-Board-Konzept, bei dem beispielsweise eine Standard-FR4-Leiterplatte mit einer HF-Leiterplatte kombiniert wird.

Bei der Umsetzung von Industrie 4.0 in der Leiterplatten-Industrie arbeitet AT&S intensiv an der Optimierung der Prozesse und der Produkte. Dank modernster Informations- und Kommunikations-Technologien können die Daten für die Produktionsprozesse in Echtzeit erfasst und verarbeitet werden, um die Prozesse zu optimieren. So werden einerseits neue Produkte erst möglich, während die Nachverfolgbarkeit den Einsatz von Ressourcen wie Materialien, Wasser oder Energie optimiert und menschliche Fehler reduziert. Letztendlich wird damit auch ein wesentlicher Beitrag zum Umweltschutz geleistet. Eine enge Zusammenarbeit mit den Kunden und Lieferanten gewährleistet zudem hochwertige und kosteneffiziente Produkte.

Bei AT&S widmen sich weltweit zurzeit rund 400 Mitarbeiter der Forschung und Entwicklung (R&D). Im Rahmen der Konferenz wurden auch weitere aktuelle Themenstellungen der Leiterplattenindustrie wie Datenaufbereitungen, Design-for-Manufacturing, Anforderungen an Leiterplatten aus Sicht eines OEM, effiziente Umsetzung von Spezifikationen oder Vor- und Nachteile verschiedener Oberflächen diskutiert.

News teilen:

Weitere Meldungen